Zynq-7000 CPU时钟编程模型是一种灵活且强大的机制,允许用户根据应用需求精确配置和调整CPU时钟频率。该模型基于一系列可编程的寄存器和控制器,通过调整这些寄存器的值,用户可以实现CPU时钟的分频、倍频以及时钟源的选择。

在Zynq-7000中,CPU时钟编程模型主要涉及到以下几个关键组件:

一、Branch时钟生成器

时钟控制器负责管理和分发时钟信号。它接收来自PLL和分频器的时钟信号,并根据配置将这些信号路由到不同的模块和系统。对于CPU时钟,时钟控制器通常负责选择时钟源、设置分频系数以及启动或停止时钟信号。

每个时钟生成器都有一个时钟控制寄存器_CLK_CTRL。在时钟控制寄存器中,SRCSEL字段用于选择时钟源,DIVISOR字段用于设置源时钟的分频系数,以产生所需的时钟频率。一些时钟生成器具有两个级联的分频器。

为了防止时钟生成器超过所连接子系统的最大频率,需要按照以下三个步骤来设置SRCSEL和DIVISOR的值:

1、根据需要增加DIVISOR的值,以确保两个PLL(相位锁环)时钟源不会导致时钟生成器超过子系统的最大时钟频率。

2、将SRCSEL设置为所需的时钟源。

3、更新DIVISOR为所需的分频系数值。

遵循上述步骤,可以确保在编程时钟生成器时不会超出子系统的频率限制,从而保护硬件免受潜在的损坏或不稳定性的影响。

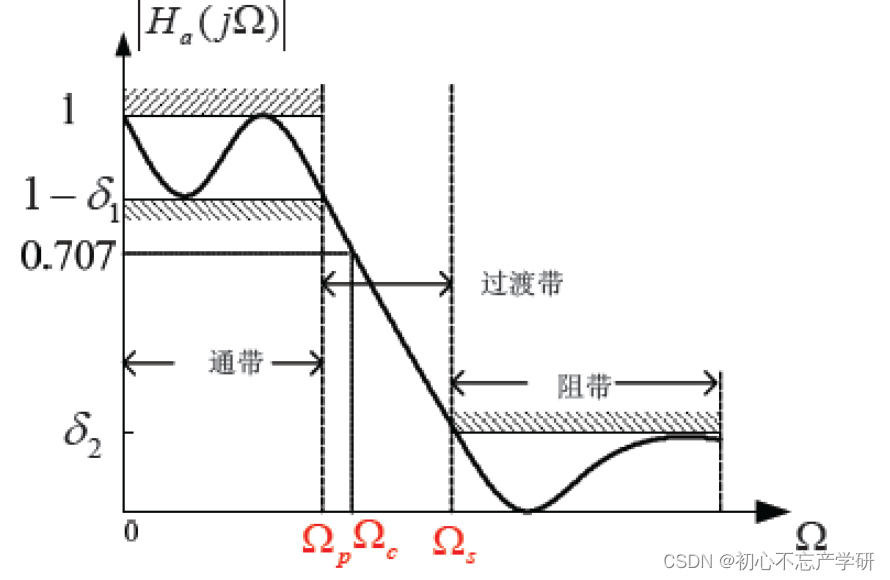

二、6位可编程分频器

6位分频器提供了从1到63的分频范围,支持偶数和奇数的分频值,从而产生接近50%的占空比,并且具有无抖动特性(分频值可以动态修改)。不过,有两个例外情况:DDR_3X分频器只能编程为使用偶数分频值,而当使用PLL(相位锁环)时,ARM_CLK_CTRL[DIVISOR]必须编程为2或更大的值。一些参考时钟具有一个分频器,而另一些则具有两个分频器。

三、DDR时钟

DDR_3x时钟必须始终编程为偶数分频值。

改变分频器的频率不会在时钟上产生抖动,但如果在不修改时序参数的情况下更改频率,DDR控制器不一定会正确运行。因此,建议在重新编程DDR时钟时,首先使DDR控制器处于空闲状态。

四、PLLs(相位锁环)

在Zynq-7000中,三个PLL共享时钟输入信号PS_CLK。每个PLL都可以在软件控制下单独旁路。作为上电复位序列的一部分,所有PLL都可以使用pll_bypass引导模式引脚绑带进行旁路。

PLL的配置和控制寄存器位于SLCR(系统级控制寄存器)中。

1、当PLL旁路模式引脚绑定为高时启用PLL模式

系统在旁路模式下启动后,可以按照以下顺序启用PLL。每个PLL都可以单独启用。此示例说明如何启用Arm PLL:

①、将ARM_PLL_CTRL[PLL_FDIV]的值和PLL配置寄存器ARM_PLL_CFG[LOCK_CNT, PLL_CP, PLL_RES]编程为所需的值。

②、通过向ARM_PLL_CTRL[PLL_BYPASS_FORCE, 4]写入1并将ARM_PLL_CTRL[PLL_BYPASS_QUAL, 3]位设置为0,强制将PLL置于旁路模式。这将取消对Arm PLL的复位。

③、通过向ARM_PLL_CTRL[PLL_RESET, 0]写入1然后写入0,来断言和取消断言PLL复位。

④、通过读取PLL_STATUS[ARM_PLL_LOCK, 3]来验证PLL是否已锁定。

⑤、通过向ARM_PLL_CTRL[4]写入0来禁用PLL旁路模式。

DDR和I/O PLL的编程方式与此类似。

2、软件控制的PLL更新

软件更新PLL时钟频率需要执行以下步骤。本示例以I/O PLL为例。表25-6显示了可能的乘法器值以及每个乘法器值所需的设置。

①、编程IO_PLL_CTRL[PLL_FDIV]的值和PLL配置寄存器IO_PLL_CFG[LOCK_CNT, PLL_CP, PLL_RES]。

②、通过向IO_PLL_CTRL[PLL_BYPASS_FORCE, 4]写入1,强制将PLL置于旁路模式。(当PLL在下一步进入复位时,其输出将是不确定的。)

③、通过向IO_PLL_CTRL[PLL_RESET, 0]写入1然后写入0,来断言和取消断言PLL复位。(这是PLL实际使用第一步中的新值的时候。)

④、通过读取PLL_STATUS[IO_PLL_LOCK, 2]来验证PLL是否已锁定。

⑤、通过向IO_PLL_CTRL[4]写入0来禁用PLL旁路模式。